电脑磁盘发出滋滋的声音,电脑磁盘有滋滋声怎么办

2023-07-17

很多朋友对异步fifo的原理 异步fifo详解不是很了解,每日小编刚好整理了这方面的知识,今天就来带大家一探究竟。

异步fifo详解

1.什么是异步FIFO

FIFO是英文First in First out的缩写。它是先进先出的数据缓冲区。与普通存储器的区别在于没有外部地址线进行读写。缺点是只能顺序读写数据(对于大数据存储,性能肯定慢),数据地址由内部读写指针自动添加,无法通过地址线来确定读写与普通内存一样,特定地址的数据,按读写是否相同时钟域分为同步和异步FIFO。这里我们主要介绍异步FIFO,它主要用于跨时钟域传输数据。

FIFO是数据缓冲区,用于实现数据先进先出的读/写模式。 FIFO有一个写端口和一个读端口,用户不需要外部控制地址,因此使用方便。 FIFO与普通Block RAM的一个明显区别是Block RAM用于数据缓存处理。用户必须自行控制读写地址的管理,并且必须保证写入的数据不包含Block RAM中未读取的内容。覆盖会导致数据错误,同时保证读取时读出未写入的地址。在使用FIFO时,只需关注FIFO控制器给出的空和满状态信号,就可以知道是否有对FIFO的错误操作,使FIFO的数据溢出或读空。

异步FIFO读写采用彼此异步的不同时钟,使用异步FIFO可以快速方便地在两个不同时钟系统之间传输实时数据

FIFO常用参数

FIFO宽度:即一次FIFO读写操作的数据位;

FIFO深度:指FIFO可以存储多少N位数据(如果宽度为N)。

满标志:当FIFO 已满或即将满时,FIFO 的状态电路发出的信号,用于防止FIFO 的写操作继续向FIFO 写入数据而导致溢出。

空标志:当FIFO 为空或即将为空时,由FIFO 的状态电路发出的信号,防止FIFO 的读操作继续从FIFO 中读取数据,导致读取到无效数据(下溢) )。

读时钟:读操作遵循的时钟,在每个时钟沿读取数据。

写时钟:写操作遵循的时钟,数据在每个时钟沿写入。

:二、设计原理

2.1 结构框图

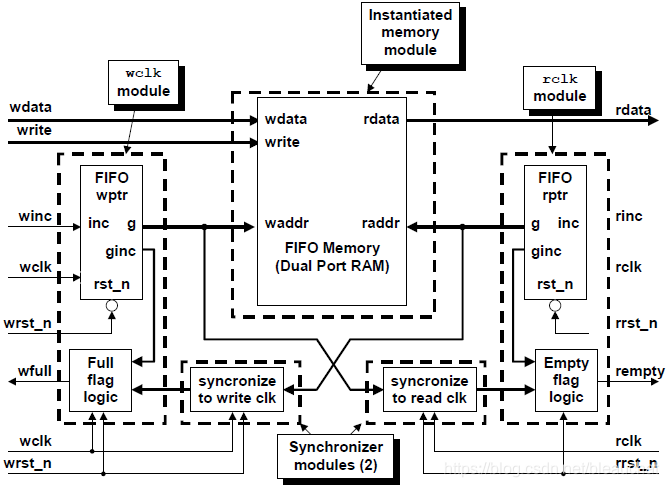

上图所示的同步模块synchronize to write clk,其作用是将读时钟域的读指针rd_ptr收集到写时钟(wr_clk)域,然后与写指针wr_ptr进行比较,产生或取消写满标志wr_full;类似具体来说,同步模块synchronize to read clk的作用是将写时钟域中的写指针wr_ptr收集到读时钟域,然后与读指针rd_ptr进行比较,生成或取消读空标志位rd_empty 。

此外,还有写指针wr_ptr和写满标志位wr_full生成模块,读指针rd_ptr和读空标志位rd_empty生成模块,以及双口存储RAM模块。

2.2 二进制计数器的问题

异步FIFO 读和写指针需要数学运算和比较来生成准确的空和满标志。然而,由于读写指针属于不同的时钟域以及读写时钟之间的相位关系的不确定性,因此同步模块从另一个时钟域收集数据。当的指针时,这个指针可能正在跳转的过程中,如下图所示,那么采集到的值很可能是一个意外的值,当然也会出现意外的错误结果。

上图中,rd_ptr2sync 3和4以及4和5之间的中间状态是由于时钟rd_clk到各个寄存器的偏差造成的。在二进制递增操作中,大多数情况下,同一次递增操作中会发生两个或多个位的变化,但由于实际电路中的时钟偏差和路径延迟不同,二进制计数器自增时不可避免地会产生错误的中间值结果,如下图所示。

由于rd_clk的上升沿在不同时间到达三个寄存器,这导致rd_ptr2sync的值在从3'b011到3'b100的转变过程中经历3'b111和3'b101,直到最后一个时钟(rd_clk0)沿后rd_ptr2sync 的到达跳转到正确的结果3'b100。虽然中间结果的持续时间较短,但这些不正确的中间结果可能会被其他时钟域的同步模块收集并导致错误的动作,如上图所示。

可见,为了避免中间结果的产生,可行的方案之一是使同步模块采集的数据逐渐变化,并且每次只变化一位。格雷码计数器是一个不错的选择。

以上知识分享希望能够帮助到大家!

版权声明:本站所有作品图文均由用户自行上传分享,仅供网友学习交流。若您的权利被侵害,请联系我们

推荐阅读

2023-07-17

2023-07-17

2023-07-17

2023-07-17

2023-07-17

2023-07-17

2023-07-17

2023-07-17

2023-07-17

2023-07-17

2023-07-17

2023-07-17

2023-07-17

栏目热点

电脑磁盘发出滋滋的声音,电脑磁盘有滋滋声怎么办

LilyGoT手表键盘C3迷你电脑套件

索泰ZBOXEdgeCI342迷你电脑正式上市

谷歌在最新的视频预告片中展示了PixelWatch的独特设计

三星与设计师Juun.J合作推出限量版可折叠产品和配件

从2023年起Fitbit设备将需要Google帐户

TOKKCAMC2+智能WiFi独立日 夜视摄像头

三星正在与全球时尚品牌JUUN.J合作

OnePlusNordWatch的颜色选项通过泄露的渲染揭示

就在第一款Nothing手机发布之前一种新的TWS芽设计浮出水面